Gate Delay (PTM-GD™)

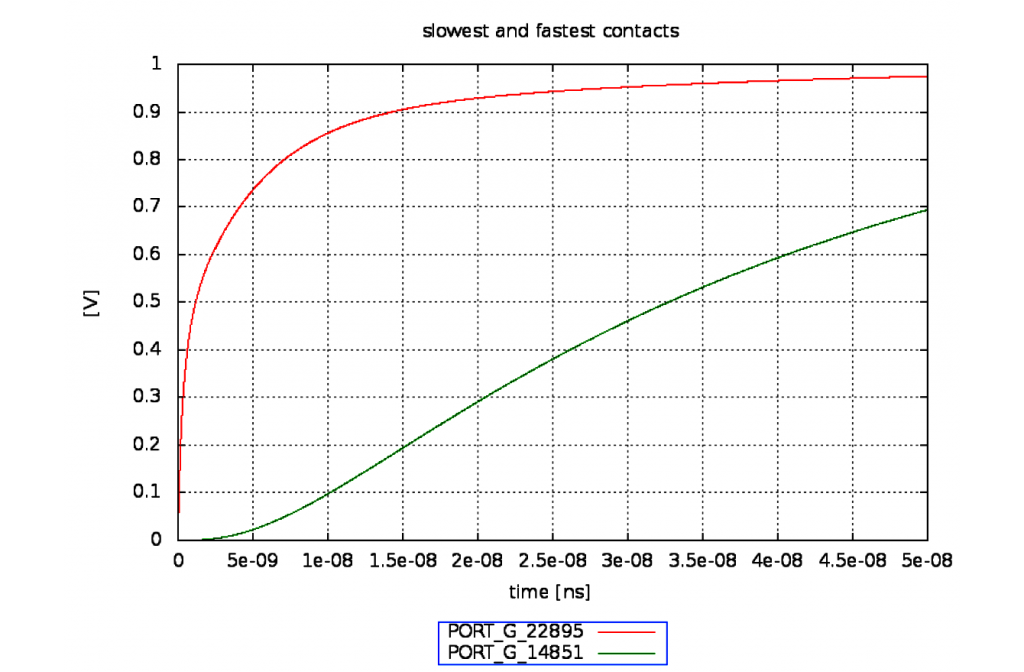

Gate delay is a critical performance characteristic of power transistors. Power transistors have very long effective gate widths, which leads to a distributed structure of complex interconnect to carry the gate signal to each switching element. Delays and non-linearities occur because of the properties of the metal and poly gate network as well as the capacitance of the oxide and gate junction. PTM-GD™ applies state of the art solver technology to rapidly and fully characterize the gate interconnect in large and massive power transistors. It works with Spectre to provide detailed information about device switching

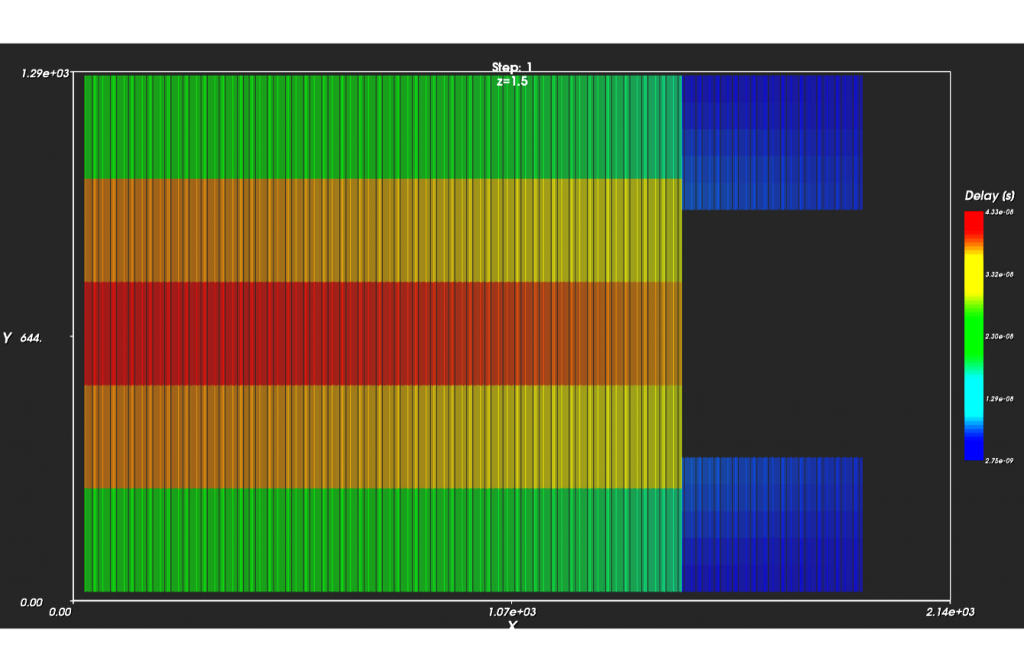

Designers can better understand the gate delay for any gate contacts in a power transistor. PTM-GD™ provides reports, graphs and color visualizations that aid in optimizing the layout of gate networks.

- PTM-GD™ models propagation delays in the gate net of power transistors

- A distributed model of the gate net is used

- Resistances in metal and poly lines are extracted

- Capacitance of active area is modeled in a distributed fashion

- Number of sections in the distributed model can be selected by the user