Magwel ESD Solutions

Years ago Magwel’s customers were looking for an ESD tool that would accurately predict ESD events and identify any overcurrent or electromigration issues. The alternative tools available at the time were too slow, overly pessimistic, not truly simulation based or simply were too hard to use for debugging ESD issues.

After working closely with customers on numerous test cases and correctly identifying parasitic device triggering, electromigration violations and other problems observed in silicon, Magwel demonstrated how well its solution works. By taking advantage of parallel processing and using TLP data to properly simulate snap back behavior, excellent results could be obtained quickly and matched silicon behavior extremely well. The downstream cost of missing these issues in a design can include on-tester failures, respins and even field failures.

The capabilities of the tool continue to lead the industry in part due to developing ESDi-XL on foundation technology developed after Magwel spun out of IMEC. Working with customers on difficult test cases and their design problems, Magwel has added support for multiple device triggering and simulation for parallel current paths during an ESD event. This is different from just substituting R values for the active devices and assuming only one current path exists, as is done in some other products.

The simulator in ESDi-XL uses the TLP I/V data for each device to see if the device is actually triggered and what the final-state voltage drop and current is. The triggering of devices is based on whether the voltage built-up over the device during an ESD event exceeds the Vt1 voltage. The algorithm correctly models competitive triggering of parallel devices with different Vt1. This requires fully extracting and incorporating the interconnect resistance along the ESD paths as well. These are not simple point-to-point resistances; instead the tool uses multi-point resistances where the current in one current branch will affect the effective resistance seen in another.

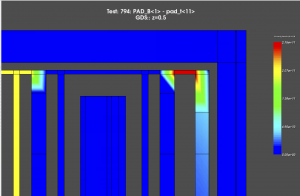

Set up is easy, with ESDi-XL obtaining stack-up information from the foundry supplied ITF file and reading TLP data in csv format. Running the tool and debugging is easy too with cross probing from the violation list to the layout with EM data overlaid in color to highlight errors.

Magwel is working on solving the issues that affect a large number of semiconductor companies and whose effects can frequently be tied to yield, reliability and performance.