ESD HBM Protection Network Verification (ESDi)

Magwel offers breakthroughs in HBM ESD analysis with its revolutionary ESDi product.

Download the ESDi Data Sheet

For HBM, ESDi thoroughly simulates all pin combinations in a design for comprehensive ESD event protection. Chips with large numbers of pins are analyzed extremely quickly using parallel processing and optimizations that preserve accuracy and boost speed.

ESDi automatically identifies and extracts the ESD network, including all supply nets. Unlike rule based tools, ESDi uses extraction and simulation engines specifically designed for ESD verification to analyze the circuit layout and protection devices. It also does a better job than conventional circuit simulators because they do not handle snap-back modeling well.

“It’s the workhorse tool now for ESD reviews”

“A junior engineer using ESDi is able to do the work of a senior ESD engineer”

“About 50% of the designs that come through the team get sent back to design team to fix problems found by ESDi” – – Leading RF Chip Company

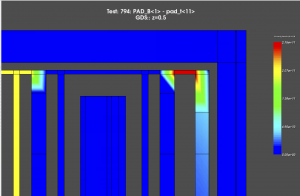

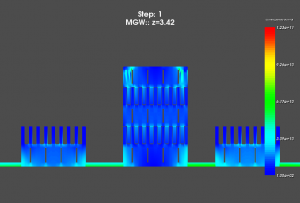

ESDi simulates multiple ESD device triggers per event which provides accurate current values on all discharge paths using precise extracted parasitics for the full ESD protection network. EM-violations, high R and IR-drops, device voltage- and current-stress, oxide-breakdown, junction damage, parasitic substrate currents, etc are checked and reported through the user interface or graphically.

The ESDi GUI offers an integrated layout editing tool to help users test and experiment with layout changes to address ESD and current density errors. ESDi makes it easy to change layout and quickly rerun all ESDi analysis and simulation to rapidly find effective fixes for ESD issues. The layout editor tool can be used to change or add metal lines, add or remove vias, and make other layout changes. This time saving ability eliminates tedious iterations that would otherwise be required.

- Chip-level 3D ESD-network extraction & verification

- Runs ESD compliance tests on all pad combinations

- Supports multiple power / ground domains and pad groups

- Includes layout of ESD cells in extraction

- Reports Bus and interconnect resistances, voltage and current stress over devices and electro-migration violations

- Fully simulates 100’s of pin pairs in a chip-level ESD network in just hours

- Supports multi-threading