# **3D Solver Based Power Transistor Electro-Thermal Modeling**

**PTM-ET**

Increase Productivity - Avoid Respins, Field Failures, & Over Design

Thermal considerations are extremely important during the design of power devices. Correctly locating sense devices and thermal planning can become trial and error efforts. It is important to find optimum locations for sense devices that reflect the conditions within larger power devices. Also, thermal planning can't wait until device design is complete. Without the ability to simultaneously understand thermal and electrical behavior, respins and redesgin can delay projects.

PTM-ET removes the guesswork from thermal design of power transistors. The operating temperature within a device depends on internal and external factors. Internally there is joule heating in the active area and in poly and metal interconnect. Externally there can be nearby heat sources and outward conduction through the substrate, bond-wire, package and PCB.

PTM-ET simulates the operation of the device based on user defined electrical stimulus. Because electrical operation is also dependent on temperature, mutually dependent thermal and electrical equations are solved simultaneously to arrive at the most accurate thermal and electrical solution. This eliminates any need to iterate back and forth between tools.

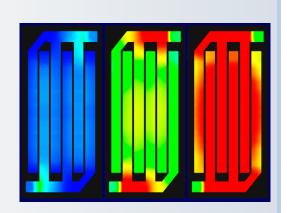

The highly accurate Field View visualizes the variation in temperature and current density over the device in 2D and 3D. With this visual feedback it is possible validate sense device placement and identify sources of current crowding.

PTM-ET takes advantage of its all-angle mesher and 64 bit solver to provide highly accurate and silicon correlated results for all aspects of device operation.

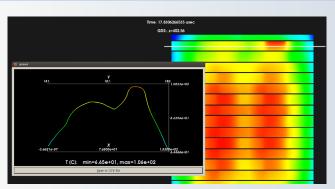

PTM-ET shows temperature rise over time with device excitation

## **PTM-ET Capability Highlights**

- Assists in finding optimal location for replicas

- · Enables package selection and thermal planning early in the design process

- · Combines thermal and electrical operation in a single solution

- Highlights temperature gradients and peak temperature

- Helps locate hot spots and avoid thermal runaway conditions

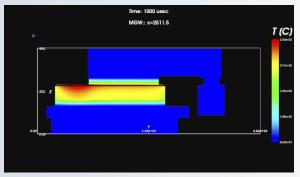

- Considers thermal flows in the chip, package and PCB

## Concurrent Thermal and Electrical Equation Solution

PTM-ET uses foundry SPICE models to obtain nonlinear models for the active areas. Joule heating is combined with thermal models for heat flow in the device, substrate, lead frame, bond wires, package and PCB. Non-linear equations are solved using advanced algorithms giving a detailed spacial view of temperature during device operation.

Side view visualization helps identify hot spots

### **Features**

- True 3D simulation accuracy with state-of-theart sparse matrix iterative solvers

- 3D visualization of results to help identify hot spots that can lead to thermal runaway

- Efficient mesh generator for large, complex 3D structures containing transistors with channel widths of several meters

- Powerful 2D and cross-cut viewing of current densities, voltage and thermal data. Display of lds, Vds and voltage drops along channels, plus textual output in csv files

- Precisely models wedge-shaped, rounded & other non-Manhattan layouts, metal slotting, and circular and diamond shaped vias

- Supports CMOS, DMOS (lateral and vertical) & IGBT power devices, honeycomb, serpentine and other layout architectures

Cross section temperatures at any slice can be plotted for analysis

# **Power Transistor Modeling Suite**

PTM is part of a comprehensive family of tools available from Magwel for modeling all aspects of power transistor behavior and performance. Designing competitive power devices requires a thorough understanding of the timing, transient and electro-thermal behavior of power transistors.

### **PTM - Power Transistor Modeler**

Using its 3D all-angle mesh solver, PTM extracts Rdson for power transistors. It reports and graphically shows current densities, power dissipation and electromigration violations.

### PTM-GD - Gate Delay

Switching in power transistors depends on the RC characteristics of the metal and poly gate interconnect. PTM-GD uses its highly accurate solver to extract distributed RC models for the gate interconnect and device capacitance. This information is used to predict turn-on/off time for power transistors that have very large gate widths.

### PTM-TR - Transient

Solving transient behavior in power transistors requires understanding both the metalization and the device physics. PTM-TR produces Fast3D models for Virtuoso ADE co-simulation to provide a complete picture of dynamic device switching behavior.

### PTM-ET - Electro-Thermal

PTM-ET combines interconnect and device joule heating with other heat sources and sinks to determine device thermal behavior. PTM-ET concurrently and dynamically models device thermal and electrical performance for devices in their packaging using stimulus to provide an accurate view during circuit operation over time.

> Magwel NV Vital Decosterstraat 44, bus 27 3000 Leuven, Belgium +32 16 43 81 13

> > www.magwel.com